Защелки в Digital Logic

Защелки - это основные элементы памяти, которые работают с уровнями сигналов (а не с переходами сигналов). Защелки, управляемые часовым переходом, являются триггерами. Защелки - это устройства, чувствительные к уровню. Защелки полезны для проектирования асинхронной последовательной схемы.

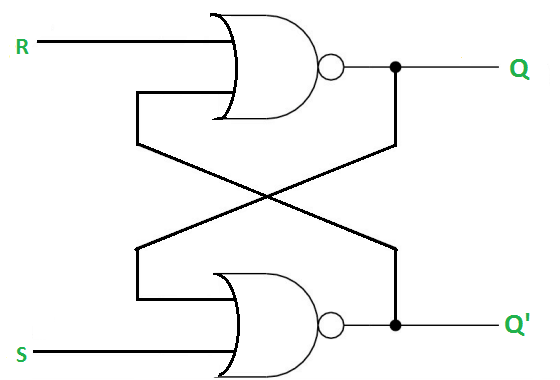

Защелка SR (Set-Reset) - Защелка SR представляет собой схему с:

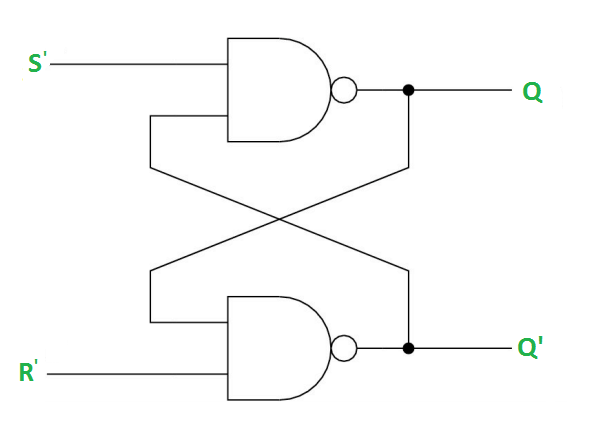

(i) 2 затвора ИЛИ-НЕ с перекрестной связью или 2 затвора И-НЕ с перекрестной связью.

(ii) 2 входа S для SET и R для СБРОСА.

(iii) 2 выхода Q, Q '.

| Q | Q ' | ШТАТ |

|---|---|---|

| 1 | 0 | Установленный |

| 0 | 1 | Сброс настроек |

В нормальных условиях оба входа остаются равными нулю. Ниже приводится защелка RS с логическими элементами NAND:

Случай-1: S '= R' = 1 (S = R = 0) -

Если Q = 1, входы Q и R 'для второго логического элемента И-НЕ оба равны 1.

Если Q = 0, входы Q и R 'для второго логического элемента И-НЕ равны 0 и 1 соответственно.

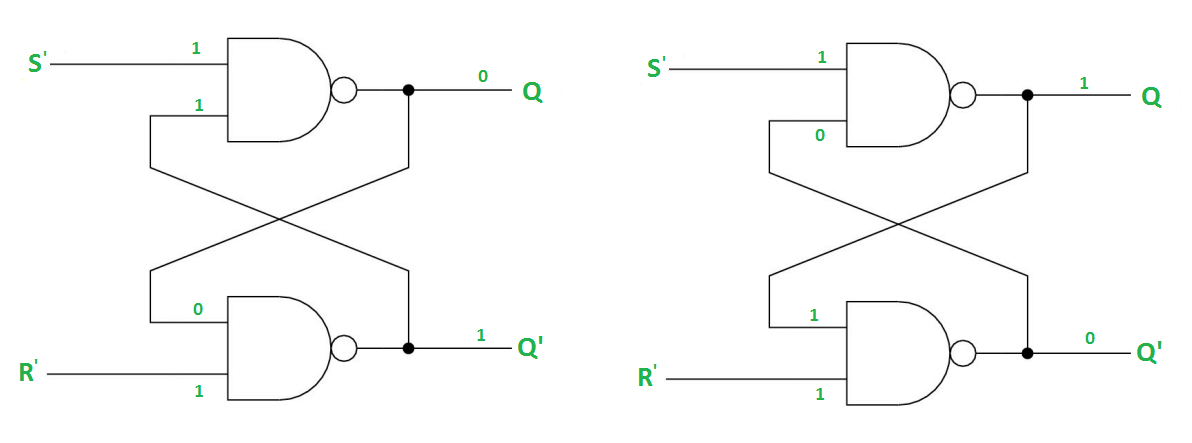

Случай-2: S '= 0, R' = 1 (S = 1, R = 0) -

Поскольку S '= 0, выход 1-го логического элемента И-НЕ, Q = 1 ( состояние SET ). Во втором логическом элементе И-НЕ, поскольку входы Q и R 'равны 1, Q' = 0.

Случай-3: S '= 1, R' = 0 (S = 0, R = 1) -

Поскольку R '= 0, выход 2-го логического элемента И-НЕ, Q' = 1. В 1-м вентиле И-НЕ, поскольку входы Q и S 'равны 1, Q = 0 ( состояние СБРОС ).

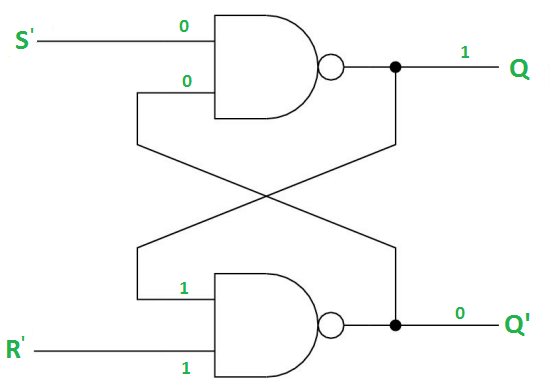

Случай-4: S '= R' = 0 (S = R = 1) -

Когда S = R = 1, Q и Q 'становятся 1, что недопустимо. Итак, условие ввода запрещено.

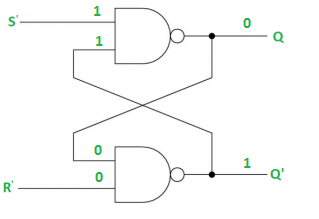

Защелка SR, использующая вентиль NOR, показана ниже:

Защелка закрытого типа SR -

Защелка Gated SR - это защелка SR с входом включения, которая работает, когда enable равно 1, и сохраняет предыдущее состояние, когда enable равно 0.

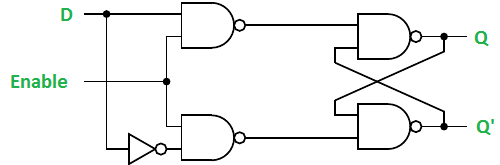

Защелка закрытая D -

Защелка D аналогична защелке SR с некоторыми изменениями. Здесь входы дополняют друг друга. Конструкция D-защелки с сигналом включения приведена ниже:

Таблица истинности для D-защелки показана ниже:

| Давать возможность | D | Q (п) | Q (п + 1) | ШТАТ |

|---|---|---|---|---|

| 1 | 0 | Икс | 0 | СБРОС НАСТРОЕК |

| 1 | 1 | Икс | 1 | УСТАНОВЛЕННЫЙ |

| 0 | Икс | Икс | Q (п) | Без изменений |

Поскольку выход такой же, как вход D, защелка D также называется прозрачной защелкой. Учитывая таблицу истинности, характеристическое уравнение для D-защелки с разрешающим входом можно представить в виде:

Q (n + 1) = EN.D + EN'.Q (n)

Ссылка:

ЦИФРОВАЯ ЭЛЕКТРОНИКА - Атул П. Годзе, г-жа Дипали А. Годзе