Схема (комбинированная и последовательная) Реализация с использованием Пролога

Предварительное условие – Пролог | Введение

Обзор :

Цифровые схемы или цифровая электроника — это отрасль электроники, которая имеет дело с цифровыми сигналами для выполнения различных задач для удовлетворения различных требований. Входной сигнал, применяемый к этим схемам, имеет цифровую форму, которая представлена в двоичном формате 0 и 1. Эти схемы разработаны с использованием логических вентилей, таких как вентили И, ИЛИ, НЕ, НЕНАД, ИЛИ, исключающее ИЛИ, которые выполняют логические операции. Это представление помогает схеме переключаться из одного состояния в другое для обеспечения точного вывода. Системы с цифровыми схемами в основном предназначены для преодоления недостатков аналоговых систем, которые работают медленнее, а полученные выходные данные могут содержать ошибку. Существует два типа цифровых схем: комбинационная схема и последовательная схема.

Реализация с использованием Пролога:

Пролог — логический и декларативный язык программирования. Само название, Prolog, является сокращением от Programming in Logic.

Пример :

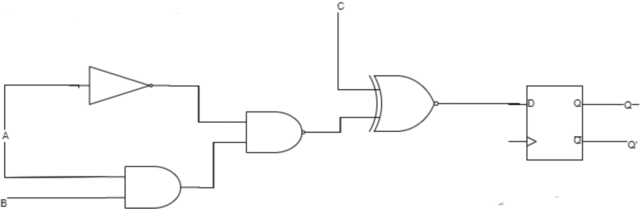

Здесь возникает вопрос, как изобразить схему в коде пролога. Рассмотрим следующую принципиальную схему.

На принципиальной схеме есть 3 входа: A, B и C. Мы рассмотрим и передаем приведенную выше принципиальную схему как код пролога в следующей строке кода следующим образом.

circuit1(A,B,C,Q,R):-

not(A,T1),

and(A,B,T2),

nand(T1,T2,T3),

xnor(T3,C,T4),

dff(T4,Q,R).Описание :

Здесь Q и R — выходные переменные. T1-T4 — значения экземпляра или выходы промежуточных ворот. Используемые логические элементы: НЕ, И, НЕ-И и XNOR. Имеется один D-FLIP FLOP и 2 выхода Q и Q'. Мы будем рассматривать таблицы истинности как факты, а принципиальную схему как правила в прологе, как написано в следующем коде.

Примечание -

В следующем коде таблицы истинности написаны для g-prolog. В swi-prolog таблицы истинности предопределены.

Реализация кода:

Здесь мы реализуем логику и напишем код на прологе.

Шаг 1 :

Здесь мы реализуем таблицы истинности всех логических вентилей для двух входов A и B.

% Made by - Maninder kaur % Following are the truth tables of all logic gates for 2 inputs A and B. and(0,0,0). and(0,1,0). and(1,0,0). and(1,1,1). or(0,0,0). or(0,1,1). or(1,0,1). or(1,1,1). not(0,1). not(1,0). nand(0,0,1). nand(0,1,1). nand(1,0,1). nand(1,1,0). nor(0,0,1). nor(0,1,0). nor(1,0,0). nor(1,1,0). xor(0,0,0). xor(0,1,1). xor(1,0,1). xor(1,1,0). xnor(0,0,1). xnor(0,1,0). xnor(1,0,0). xnor(1,1,1).

Шаг 2 :

Здесь мы реализуем таблицы истинности OR GATE для 4 входов A, B, C и D.

% Following is the truth tables of OR GATE for 4 inputs A ,B ,C and D. % (Used in 8X3 Encoder) or4(0,0,0,0,0). or4(0,0,0,1,1). or4(0,0,1,0,1). or4(0,0,1,1,1). or4(0,1,0,0,1). or4(0,1,0,1,1). or4(0,1,1,0,1). or4(0,1,1,1,1). or4(1,0,0,0,1). or4(1,0,0,1,1). or4(1,0,1,0,1). or4(1,0,1,1,1). or4(1,1,0,0,1). or4(1,1,0,1,1). or4(1,1,1,0,1). or4(1,1,1,1,1).

Шаг 3 :

Здесь мы реализуем половинный сумматор.

% HALF ADDER :-

% INPUT VARIABLES - A,B,C

% OUTPUT VARIABLES - S ,Ca(Sum and Carry)

half_adder(A,B,S,Ca):-

xor(A,B,S),

and(A,B,Ca).Шаг-4:

Здесь мы реализуем полный сумматор.

%FULL ADDER :-

%INPUT VARIABLES - A,B,C

%OUTPUT VARIABLES - S ,Ca (Sum and Carry)

full_adder(A,B,C,S,Ca):-

xor(A,B,T1),

xor(C,T1,S),

and(T1,C,T2),

and(A,B,T3),

or(T3,T2,Ca).Шаг-5:

Здесь мы реализуем половинный вычитатель.

% HALF SUBTRACTOR :-

% INPUT VARIABLES - A,B

% OUTPUT VARIABLES - D ,BO (Difference and borrow)

half_sub(A,B,D,BO):-

xor(A,B,D),

not(A,T1),

and(B,T1,BO).Шаг-6:

Здесь мы реализуем полный вычитатель.

% FULL SUBTRACTOR :-

% INPUT VARIABLES - A,B

% OUTPUT VARIABLES - D ,BO (Difference and borrow)

full_sub(A,B,BI,D,BO) :-

xor(A,B,T1),

xor(T1,BI,D),

not(T1,T2),

not(A,T3),

nand(T2,BI,T4),

nand(T3,B,T5),

nand(T4,T5,BO).

Шаг-7:

Теперь мы реализуем ДЕКОДЕР 2 × 4.

% 2 X 4 DECODER

% INPUT VARIABLES - A,B

% OUTPUT VARIABLES - D0,D1,D2,D3

decoder_2x4(A,B,D0,D1,D2,D3):-

not(A,A_0),

not(B,B_0),

and(A_0,B_0,D0),

and(A_0,B,D1),

and(A,B_0,D2),

and(A,B,D3).Шаг 8:

Теперь мы реализуем ДЕКОДЕР 3 × 8.

% 3 X 8 ENCODER

% OUTPUT VARIABLES - A,B

% INPUT VARIABLES - D0,D1,D2,D3,D4,D5,D6,D7

encoder_8x3(_,D1,D2,D3,D4,D5,D6,D7,A,B,C):-

or4(D1,D3,D5,D7,A),

or4(D2,D3,D6,D7,B),

or4(D4,D5,D6,D7,C).Шаг-9:

Теперь мы реализуем МУЛЬТИПЛЕКСОР 2 X 1.

% 2 X 1 MULTIPLEXER

% INPUT VARIABLES - A,B,S (Selector)

% OUTPUT VARIABLES - Z

mux_2x1(A,B,S,Z):-

not(S,S1),

and(A,S1,I0),

and(B,S,I1),

or(I0,I1,Z).Шаг-10:

Теперь мы реализуем демультиплексор 1 × 2.

% 1 X 2 DEMULTIPLEXER

% INPUT VARIABLES - I (Input) ,S (Selector)

% OUTPUT VARIABLES - A,B

demux_1x2(I,S,A,B):-

not(S,S_0),

and(I,S_0,A),

and(I,S,B).Шаг 11:

Теперь мы реализуем демультиплексор 1 × 4.

% 1 X 4 DEMULTIPLEXER

% INPUT VARIABLES - I (Input) ,S0 and S1(Selectors)

% OUTPUT VARIABLES - A,B,C,D

demux_1x4(I,S0,S1,A,B,C,D):-

decoder_2x4(S0,S1,T0,T1,T2,T3),

and(I,T0,A),

and(I,T1,B),

and(I,T2,C),

and(I,T3,D).Шаг 12:

Теперь мы реализуем D FLIP FLOP.

% D FLIP FLOP TRUTH TABLE dff(0,0,1). dff(1,1,0).

Шаг 13:

Теперь мы реализуем код схемы.

% CIRCUITS

circuit1(A,B,C,Q,R):-

not(A,T1),

and(A,B,T2),

nand(T1,T2,T3),

xnor(T3,C,T4),

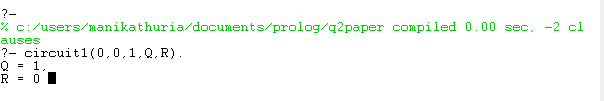

dff(T4,Q,R).Выход :