Соединение QuickPath

Ранее я писал о технологии HyperTransport, разработанной AMD для увеличения скорости передачи данных. Ключевой особенностью HyperTransport является то, что это двухточечная система межсоединений, а не шинная система. В этой статье я расскажу о конкуренте HyperTrasport — Intel QuickPath Interconnect.

Передняя боковая шина

Прежде чем я объясню, что такое QuickPath Interconnect, я сделаю шаг назад и объясню, на что похожа традиционная архитектура связи между чипами в компьютерах. В течение многих лет для связи между процессорами и памятью в компьютерах использовалась так называемая шина Front Side Bus. Все коммуникации между ЦП и памятью должны проходить через одну и ту же переднюю шину. Поскольку все сообщения проходят через переднюю шину, для обеспечения надлежащего обмена данными должны быть добавлены некоторые дополнительные данные; например, адресация.

Кроме того, шинные системы по своей конструкции позволяют осуществлять только одну связь за раз. Это означает, что если что-то нуждается в связи с ЦП, оно должно дождаться завершения текущей связи, чтобы начать свое собственное взаимодействие. В качестве альтернативы прерывания могут использоваться для приоритетной связи. Прерывания, хотя и эффективны, также добавляют некоторую нагрузку на общий обмен данными по внешней шине. Все это ожидание в сочетании с накладными расходами может стать препятствием для производительности высокоскоростных приложений.

За последние несколько лет, когда процессоры значительно увеличили свою производительность, скорость, с которой могла работать шина, стала фактором, ограничивающим общую производительность компьютера. Это связано с тем, что, несмотря на то, что процессор мог выполнять большую часть работы очень быстро, ему приходилось постоянно ждать, пока передняя шина обеспечит надлежащую связь; поэтому процессор часто простаивал. Скорость Front Side Bus также делала бессмысленной скорость RAM, поскольку скорость, с которой могла работать RAM, была значительно выше, чем максимальная скорость Front Side Bus.

При более широком использовании нескольких процессоров, включая мощные и производительные графические процессоры, и очень быстрой памяти ограничения шины Front Side Bus становятся немного нелепыми. Это послужило толчком для разработки таких технологий, как HyperTransport, которая представляет собой систему межсоединений «точка-точка» и, следовательно, устраняет многие ограничения внешней шины, такие как прерывания и адресация (вам действительно не нужна адресация, когда есть только две точки). – если вы его не отправляли, то должны были получить!).

Соединение QuickPath

Но HyperTransport, разработанная AMD и теперь управляемая консорциумом HyperTransport, — не единственная игра в городе. Неудивительно, что Intel разработала собственную систему межсетевого взаимодействия «точка-точка», оптимизированную для работы в качестве механизма связи между многими процессорами. Хотя они значительно позже разработали QuickPath Interconnect, они проделали большую работу.

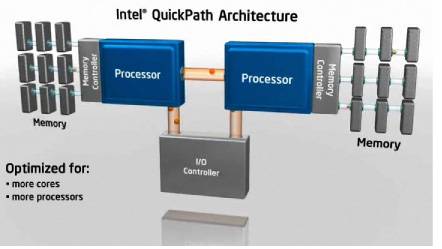

Рис. 1. Архитектура QuickPath предоставлена www.intel.com

Как и HyperTransport, QuickPath Interconnect предназначен для работы с процессорами со встроенными контроллерами памяти. Как и HyperTransport, QuickPath Interconnect разработан как технология с удвоенной скоростью передачи данных (DDR). Обычно, когда данные передаются в цифровом виде между двумя точками, данные считываются либо как высокие, либо как низкие, что представляет либо 1, либо 0. Эти данные считываются всякий раз, когда часы выдают высокий сигнал. В DDR данные можно считывать по переднему и заднему фронтам тактового сигнала. Это означает, что за один полный тактовый цикл данные передачи, поддерживающие DDR, могут быть считаны дважды, что в два раза увеличивает скорость передачи данных.

Также как и HyperTransport, QuickPath Interconnect уменьшает накладные расходы, характерные для архитектур Front Side Bus. Один из способов сделать это — исключить некоторую адресацию, поскольку QuickPath Interconnect — это технология «точка-точка». Фактически QuickPath Interconnect является не только технологией «точка-точка», но и полнодуплексным каналом связи, имеющим 20 выделенных каналов связи для каждого направления. Однако QuickPath Interconnect имеет некоторые накладные расходы. QuickPath Interconnect на самом деле имеет больше накладных расходов, чем Hypertransport; для отправки 64 бит данных QuickPath Interconnect требует 16 бит служебных данных, тогда как HyperTransport требует 8 или 12 бит для чтения и записи соответственно.

Слои портокола

Intel QuickPath Interconnect является частью более крупной архитектуры, которую Intel называет архитектурой QuickPath. Архитектура QuickPath предназначена для покрытия пяти сетевых уровней, которые примерно эквивалентны некоторым сетевым уровням OSI.

Физический уровень архитектуры QuickPath описывает физическую разводку соединений, включая передатчики и приемники данных, а также 20-битные полосы в каждом направлении.

Связной слой архитектуры QuickPath описывает фактическую отправку и получение данных в 72-битных разделах с 8-битными, используемыми для обнаружения ошибок CRC. Это составляет в общей сложности 80 бит, которые передаются по каждой из 20 полос в каждом направлении!

Уровень маршрутизации отвечает за отправку 72-битного фрагмента данных на канальный уровень. Внутри этого 72-битного фрагмента данных находятся 64-битные данные и 8-битный заголовок. 8-битный заголовок состоит из пункта назначения и типа сообщения. Эти 64-разрядные значения используются Intel для расчета общей пропускной способности соединения QuickPath Interconnect (в отличие от всех 80-разрядных).

Транспортный уровень отвечает за обработку ошибок при передаче данных и будет запрашивать повторную передачу в случае обнаружения ошибок.

Уровень протокола архитектуры QuickPath обеспечивает согласованность кэша, а также то, как программа более высокого уровня будет получать доступ к механизмам передачи данных в QuickPath Interconnect.

Интерконнект QuickPath и HyperTransport

Итак, теперь, когда вы узнали о QuickPath Interconnect и ознакомились с моей предыдущей статьей о HyperTransport, у вас должно быть хорошее представление о том, как отрасль отходит от архитектуры Front Side Bus — на благо всех нас. Но вы, вероятно, задаетесь вопросом, какая технология лучше. Как обычно, на этот вопрос сложно ответить. В настоящее время кажется, что QuickPath Interconnect имеет небольшое общее преимущество в производительности по сравнению с HyperTransport, но HyperTransport разработан как гораздо более гибкая технология.

QuickPath Interconnect в основном предназначен для подключения нескольких процессоров друг к другу и к контроллеру ввода/вывода, как показано на рисунке 1 выше. HyperTransport делает это, но его также можно использовать для дополнительных плат и в качестве механизма передачи данных в маршрутизаторах и коммутаторах. HyperTransport также является открытой технологией, что, как мне кажется, дает ей значительное преимущество перед QuickPath Interconnect, технологией Intel. Однако это все еще ранняя разработка обеих этих технологий; особенно для соединения QuickPath. В течение следующих нескольких лет вы начнете видеть, как эти технологии интегрируются во все больше и больше компьютеров, и вы, вероятно, увидите некоторые инновации в каждом из этих продуктов, которые повышают их производительность. Что касается QuickPath Interconnect, я также ожидаю увидеть некоторую диверсификацию способов его использования, чтобы он действительно мог конкурировать с HyperTransport в качестве механизма передачи данных для многих целей.