4-битный двоичный декрементер

Опубликовано: 25 Сентября, 2022

Что такое 4-битный двоичный декрементатор?

Он вычитает 1 двоичное значение из существующего двоичного значения, хранящегося в регистре, или, другими словами, мы можем просто сказать, что оно уменьшает существующее значение, хранящееся в регистре, на 1.

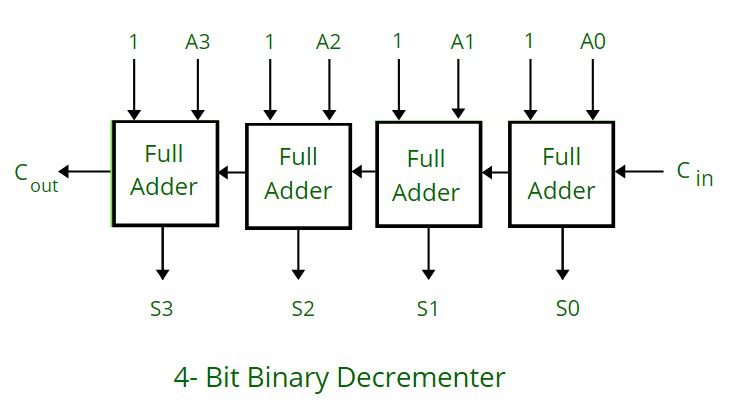

Для любого n-битного двоичного декрементатора 'n' относится к емкости регистра, который необходимо уменьшить на 1. Таким образом, нам требуется 'n' число полных сумматоров. Таким образом, в случае 4-битного двоичного декрементора нам потребуется 4 полных сумматора.

Работающий:

- Он состоит из 4 полных сумматоров, соединенных друг за другом. Каждый полный сумматор имеет 3 входа (вход переноса, 1, A) и 2 выхода (выход переноса и S).

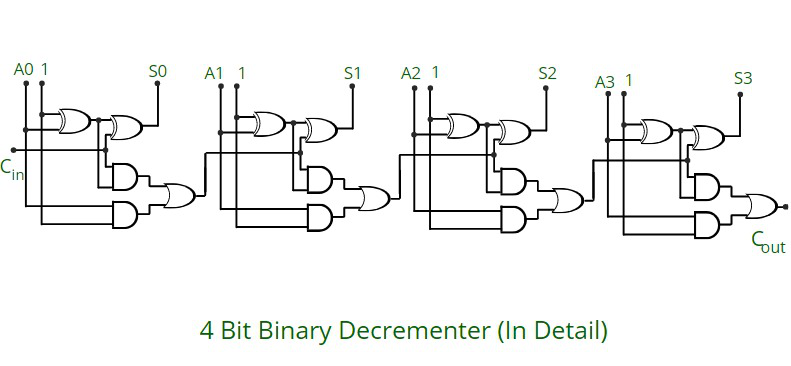

- Базовый полный сумматор состоит из 2 половинных сумматоров и вентиля ИЛИ.

- Перенос (C) от предыдущего полного сумматора распространяется на следующий полный сумматор. Таким образом, вывод переноса одного полного сумматора становится одним из трех входов следующего полного сумматора.

- Это соответствует концепции дополнения до 2, поэтому мы принимаем 1 в качестве входных данных во всех 4 полных сумматорах, как видно из приведенной выше диаграммы.

- Итак, мы добавляем 1111, чтобы вычесть 1.

Причина добавления 1111:

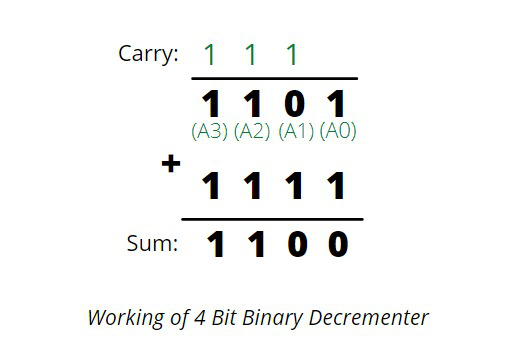

- Это потому, что наш основной мотив — вычесть 1, что в 4-битном представлении равно 0001.

- Представление его в дополнении 1 даст: 1110

- Представление его в дополнении до 2 (добавление дополнения от 1 до 1) даст: 1111

- Это причина, по которой ввод 1111 дан для получения уменьшенного вывода в 4-битном двоичном декрементере.

In 4 bit representation In 1"s complement In 2"s complement

1 -------------------------> 0001 ----------------------> 1110 ---------------------> 1111

Пример:

(Refer to the circuit diagram from right to left for better understanding)

1. Input: 1010 ----> After using 4 bit binary decrementer ----> Output: 1001

1 0 1 0 (Comparing from the circuit 1 0 1 0 is A3, A2, A1, A0 respectively)

+ 1 1 1 1 (1 1 1 1 is added as seen in the diagram also, in each full adder 1 is taken as input)

________

1 0 1 1 ( 1 0 1 1 , in the diagram are S3, S2, S1, S0 respectively)

________

2. Input: 0010 ----> After using 4 bit binary decrementer ----> Output: 0001 1 0 1 0 + 1 1 1 1 ________ 0 0 0 1 ________

3. Input: 0011 ----> After using 4 bit binary decrementer ----> Output: 0001 0 0 1 1 + 1 1 1 1 _________ 0 0 1 0 _________