Арифметико-логическое устройство

Введение

Арифметико-логическое устройство (АЛУ) по сути является сердцем процессора. Это то, что позволяет компьютеру складывать, вычитать и выполнять основные логические операции, такие как И/ИЛИ. Поскольку каждый компьютер должен иметь возможность выполнять эти простые функции, они всегда включены в ЦП. То, как компания проектирует свои ALU, оказывает значительное влияние на общую производительность их ЦП. В этой статье я дам краткое введение в некоторые основы проектирования АЛУ; вы быстро увидите, насколько сложными могут быть эти вещи.

Логические ворота

Прежде чем мы перейдем к общей конструкции АЛУ, мы должны сначала понять основы логических вентилей. На рис. 1 показаны основные логические элементы в их графическом представлении. Имейте в виду, что каждый из них можно сделать из транзисторов, комбинируя их по-разному. Какие типы транзисторов и как они расположены, могут повлиять на работу затвора.

Ворота «И»

Ворота «ИЛИ»

Ворота XOR

Ворота «НЕ»

Ворота «И-НЕ»

Ворота «НОР»

Ворота XNOR

Рисунок 1: Базовые логические вентили (любезно предоставлено wikipedia.com)

Эти логические вентили работают, принимая два входа (один вход для вентиля «НЕ») и производя выход. Если мы рассмотрим логический элемент «И», выход будет истинным, или «1» (или высоким напряжением), если вход № 1 и вход № 2 истинны, а выход будет ложным, или «0» (или высокое напряжение). низкое напряжение), если один или оба входа ложные. Точно так же, если мы рассмотрим вентиль «ИЛИ», вывод будет истинным, если истинны ввод № 1 или ввод № 2. Выход вентиля «XOR» будет истинным, если любой вход истинен, и ложным, если оба входа истинны; это реализация логической операции исключающее ИЛИ. Ворота «НЕ» будут выводить противоположное входу; поэтому, если вход истинен, выход логического элемента «НЕ» будет ложным. Элементы «И-НЕ», «НЕ-ИЛИ» и «ИСКЛЮЧАЮЩЕЕ ИЛИ» являются реализациями элементов «И», «ИЛИ» и «ИСКЛЮЧАЮЩЕЕ ИЛИ» соответственно с элементом «НЕ» перед выходом; поэтому вентиль «И-НЕ» вернет то, что вентиль «И» не вернет.

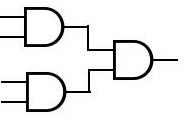

Эти логические функции сами по себе являются важной частью функциональности ЦП, но выполнение логических операций над двумя входами не столь полезно. Объединив эти вентили вместе, мы можем получить устройства с большим количеством входов. Например, на рисунке 2 я объединил три логических элемента «И». Эти три логических элемента «И» будут давать выходной сигнал, который будет истинным только тогда, когда все четыре входных сигнала будут истинными. По сути, это 4-битный логический элемент «И». Вы можете экстраполировать это и сформировать 8-битный логический элемент «И», объединив два 4-битных «И» и один 2-битный «И».

Рисунок 2: 4-битное устройство «И»

Арифметика

Комбинируя эти вентили в еще более умные конфигурации, мы можем выполнять другие полезные функции, такие как сложение. На рис. 3 показана типичная конфигурация, называемая полусумматор. Чтобы понять, как работает этот сумматор, мы должны думать о входных данных не как об истинном или ложном, а как о «1» или «0». Выход этого сумматора представляет собой сумму входов с битом переноса. Если входные данные равны «1» и «1», мы добавляем 1 плюс 1. Выход, помеченный как «СУММ», представляет собой просто «исключающее ИЛИ» входных данных, которые будут равны «0». Выход, помеченный как «CARRY», представляет собой логический элемент И, который, конечно же, будет равен «1». Таким образом, дополнительный ответ равен 10, что является двоичным сложением «1» и «1». Если входные данные равны «1» и «0», «СУММА» будет «1», а «ПЕРЕНОС» будет «0», что даст ответ 01 или просто 1.

Рисунок 3: Полусумматор

Итак, если это выполняет двоичное сложение, почему оно называется полусумматор? Это связано с тем, что для сложения двоичных чисел больше двух бит нам нужно, чтобы сумматор мог принимать бит переноса вместе с двумя входными битами. Этот полный сумматор показан на рисунке 4. Вы можете видеть, что полный сумматор представляет собой два полусумматора с одним дополнительным элементом «ИЛИ». Чтобы использовать полный сумматор для сложения двух двоичных чисел произвольного размера, вы начнете с самого правого бита, называемого младшим значащим битом (LSB) каждого числа с переносимым битом «0». Затем вы должны добавить два бита, записать сумму и использовать бит переноса в качестве бита переноса при добавлении следующих двух битов и переходе к старшим битам (MSB). Повторяя этот процесс, вы можете добавить два двоичных числа любой произвольной длины. Этот процесс известен как волновой перенос.

Рисунок 4: Полный сумматор

На рис. 5 показан полупереходник. В этом сценарии, если у нас есть вход «A», равный «1», и вход «B», равный «0», мы хотим вычесть 0 из 1. Вы можете видеть, что выход «DIFF» будет «1», а « ЗАИМСТВОВАТЬ' Вывод будет '0'. Как и полусумматор, полусумматор может использоваться для реализации полного субсумматора, как показано на рисунке 6.

Рисунок 5: Полусабвуфер

Рисунок 6: Полный сабвуфер

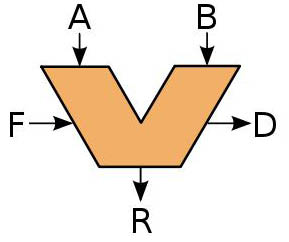

Арифметические блоки обычно группируются в АЛУ, который имеет входы, выходы и управляющие биты, которые сообщают АЛУ, какой тип операции выполнять. На рис. 7 показана типичная схема АЛУ. На этой диаграмме A и B — входы данных, F — управляющий вход для выбора функции, R — результат применения функции к A и B, а D — состояние выхода, чтобы вы знали, когда функция активна. Выполнено.

Рисунок 7: типичный ALU (символ предоставлен wikipedia.com)

Оптимизации

Пример сложения пульсирующего переноса является эффективным методом сложения двоичных чисел. Давайте немного экстраполируем это и представим 32-битный сумматор. Если мы хотим сложить два 32-битных числа, мы можем начать с младшего бита и двигаться влево, вычисляя биты переноса. Если добавление двух битов занимает пару тактов, то общее время, необходимое для добавления всех 32 битов, является значительным. К счастью, эта проблема уже решена. Решение: сумматор переноса с опережением.

В сумматоре с опережающим переносом двоичные числа разбиваются на секции, возможно, по 4 бита каждая. Теперь каждая секция может начать вычисление своих битов переноса, начиная с младшего бита секции и двигаясь к старшему биту секции. Как только бит переноса достигает старшего бита своего раздела, бит может затем перейти вперед на 4 бита за раз вместо того, чтобы двигаться к старшему биту числа по одному биту за раз. Логика, связанная с тем, чтобы все переносы оставались прямыми, довольно сложна и становится более сложной по мере увеличения размера секций; из-за этого больше времени тратится на вычисление переносов каждой секции и меньше времени на более быстрое распространение битов переноса. Однако, если размер секции слишком мал, то существует так много секций, через которые должны распространяться переносы, что экономия времени по сравнению с сумматором пульсаций переноса невелика. Выбор размера секции включает в себя подробный анализ задержек логического элемента и распространения, которые могут варьироваться в зависимости от технологии, используемой в логических элементах.

Техника переноса с опережением — это одна из оптимизаций, которую инженеры могут внести в ALU. Есть много других. Например, чтобы выполнить умножение, обычно нужно просто прибавлять число к самому себе снова и снова, но есть методы оптимизации, которые можно использовать для ускорения этого процесса. Это некоторые различия между АЛУ различных процессоров и основная причина, по которой одни процессоры лучше справляются с определенными типами операций, чем другие. Например, у графического процессора будет АЛУ, оптимизированное для арифметических операций, часто выполняемых для отображения графики, в то время как у ЦП будет АЛУ, оптимизированный для наиболее распространенных операций, выполняемых пользователями.