Кодировщик приоритетов Verilog

В схеме цифровой системы кодировщик представляет собой комбинационную схему, которая принимает 2 n входных сигнальных линий и кодирует их в n выходных сигнальных линий. Когда разрешение истинно, т. е. соответствующие линии входных сигналов отображают эквивалентный двоичный бит на выходе.

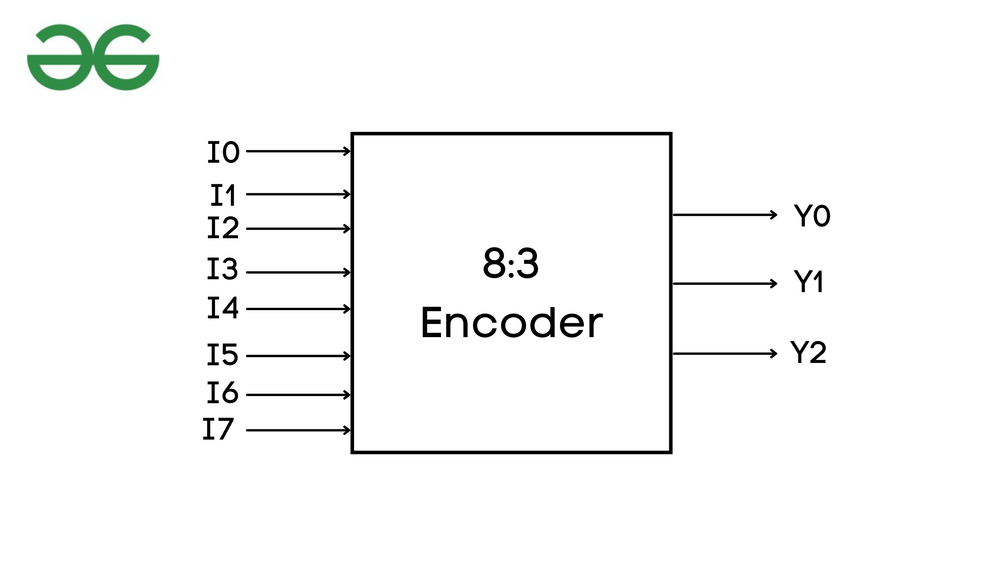

Например, энкодер 8:3 имеет 8 входных линий и 3 выходные линии, 4:2 энкодер имеет 4 входные линии и 2 выходные линии и так далее.

Кодер с приоритетом 8:3 имеет семь входных линий, т. е. от i0 до i7, и три выходные линии y2, y1 и y0. В 8:3 Priority Encoder i7 имеет самый высокий приоритет, а i0 — самый низкий.

Таблица истинности:

Вход | Выход | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| en | i7 | i6 | i5 | i4 | i3 | i2 | i1 | i0 | у2 | у1 | у0 |

| 0 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | г | г | г |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | 1 | 0 | 1 |

| 1 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 1 | 0 |

| 1 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 1 | 1 |

Логический символ:

Реализуйте кодировщик приоритетов в коде Verilog:

Большая часть программирования связана с разработкой и дизайном программного обеспечения, но Verilog HDL — это язык описания аппаратного обеспечения, который используется для разработки дизайна электроники. Verilog предоставляет разработчикам возможность разрабатывать устройства на основе различных уровней абстракции, включая: уровень шлюза, поток данных, уровень коммутатора и поведенческое моделирование.

Моделирование поведения:

Поведенческая модель, которая является высшим уровнем абстракции. Поскольку мы используем поведенческое моделирование, мы напишем код, используя if-else, чтобы обеспечить входные значения приоритетного кодировщика. При использовании условия if выходные значения назначаются на основе приоритета.

Блок дизайна: моделирование поведения

module priorityencoder_83(en,i,y);

// declare

input en;

input [7:0]i;

// store and declare output values

output reg [2:0]y;

always @(en,i)

begin

if(en==1)

begin

// priority encoder

// if condition to chose

// output based on priority.

if(i[7]==1) y=3"b111;

else if(i[6]==1) y=3"b110;

else if(i[5]==1) y=3"b101;

else if(i[4]==1) y=3"b100;

else if(i[3]==1) y=3"b011;

else if(i[2]==1) y=3"b010;

else if(i[1]==1) y=3"b001;

else

y=3"b000;

end

// if enable is zero, there is

// an high impedance value.

else y=3"bzzz;

end

endmoduleТестовый стенд: поведение

Testbench — это блок моделирования, который используется для предоставления входных данных блоку проектирования. Лучший способ написать Testbench — это иметь хорошее представление о таблице истинности. Как только у вас будет готовая таблица истинности, укажите входные значения внутри тестового стенда.

module tb;

reg [7:0]i;

reg en;

wire [2:0]y;

// instantiate the model: creating

// instance for block diagram

priorityenoder_83 dut(en,i,y);

initial

begin

// monitor is used to display the information.

$monitor("en=%b i=%b y=%b",en,i,y);

// since en and i are input values,

// provide values to en and i.

en=1; i=128;#5

en=1; i=64;#5

en=1; i=32;#5

en=1; i=16;#5

en=1; i=8;#5

en=1; i=4;#5

en=1; i=2;#5

en=1; i=0;#5

en=0;i=8"bx;#5

$finish;

end

endmoduleВыход:

Моделирование потока данных:

В моделировании потока данных мы определяем выходные данные, т. е. net, путем присвоения входных значений, т. е. reg, с использованием назначенных ключевых слов. Чтобы написать моделирование потока данных и моделирование на уровне шлюза, нам нужна логическая схема для формирования соединений.

Вот логическая схема кодера с приоритетом 8:3.

Блок дизайна: поток данных

module priorityenoder83_dataflow(en,i,y);

// declare port list via input and output

input en;

input [7:0]i;

output [2:0]y;

// check the logic diagram and assign the outputs

assign y[2]=i[4] | i[5] | i[6] | i[7] &en;

assign y[1]=i[2] | i[3] | i[6] | i[7] &en;

assign y[0]=i[1] | i[3] | i[5] | i[7] &en;

endmoduleТестовый стенд: поток данных

module tb;

reg en;

reg [7:0]i;

wire [2:0]y;

// instantiate the model: creating

// instance for block diagram

priorityenoder83_dataflow dut(en,i,y);

initial

begin

// monitor is used to display the information.

$monitor("en=%b i=%b y=%b",en,i,y);

// since en and i are input values,

// provide values to en and i.

en=1;i=128;#5

en=1;i=64;#5

en=1;i=32;#5

en=1;i=16;#5

en=1;i=8;#5

en=1;i=4;#5

en=1;i=2;#5

en=1;i=1;#5

en=0;i=8"bx;#5

$finish;

end

endmoduleВыход:

Моделирование уровня ворот:

В моделировании на уровне вентилей мы используем логические вентили Digital, используемые в цифровой электронике.

Синтаксис:

logicgate object(out,in1,in2);

Пример:

and a1(out,a,b);

Блок дизайна: уровень ворот

module priorityenoder83_gate(en,i,y);

// declare port list via input and output

input en;

input [7:0]i;

output [2:0]y;

wire temp1,temp2,temp3; // temp is used to apply

// enable for the or gates

// check the logic diagram and use

// logic gates to compute outputs

or o1(temp1,i[4],i[5],i[6],i[7]);

or o2(temp2,i[2],i[3],i[6],i[7]);

or o3(temp3,i[1],i[3],i[5],i[7]);

and a1(y[2],temp1,en);

and a2(y[1],temp2,en);

and a3(y[0],temp3,en);

endmoduleТестовый стенд: уровень ворот

module tb;

reg en;

reg [7:0]i;

wire [2:0]y;

// instantiate the model: creating

// instance for block diagram

priorityenoder83_gate dut(en,i,y);

initial

begin

// monitor is used to display

// the information.

$monitor("en=%b i=%b y=%b",en,i,y);

// since en and i are input values,

// provide values to en and i.

en=1;i=128;#5

en=1;i=64;#5

en=1;i=32;#5

en=1;i=16;#5

en=1;i=8;#5

en=1;i=4;#5

en=1;i=2;#5

en=1;i=1;#5

en=0;i=8"bx;#5

$finish;

end

endmoduleВыход:

Применение приоритетного кодировщика:

- Роботизированные транспортные средства

- Системы мониторинга здоровья в больницах